当今,在没有透彻掌握芯片、封装结构及PCB的电源供电系统特性时,高速电子系统的设计是很难成功的。事实上,为了满足更低的供电电压、更快的信号翻转速度、更高的集成度和许多越来越具有挑战性的要求,很多走在电子设计前沿的公司在产品设计过程中为了确保电源和信号的完整性,对电源供电系统的分析投入了大量的资金,人力和物力。

电源供电系统(PDS)的分析与设计在高速电路设计领域,特别是在计算机、半导体、通信、网络和消费电子产业中正变得越来越重要。随着超大规模集成电路技术不可避免的进一步等比缩小,集成电路的供电电压将会持续降低。随着越来越多的生产厂家从130nm技术转向90nm技术,可以预见供电电压会降到1.2V,甚至更低,而同时电流也会显著地增加。从直流IR压降到交流动态电压波动控制来看,由于允许的噪声范围越来越小,这种发展趋势给电源供电系统的设计带来了巨大的挑战。

PCB电源供电系统设计概览

通常在交流分析中,电源地之间的输入阻抗是用来衡量电源供电系统特性的一个重要的观测量。对这个观测量的确定在直流分析中则演变成为IR压降的计算。无论在直流或交流的分析中,影响电源供电系统特性的因素有:PCB的分层、电源板层平面的形状、元器件的布局、过孔和管脚的分布等等。

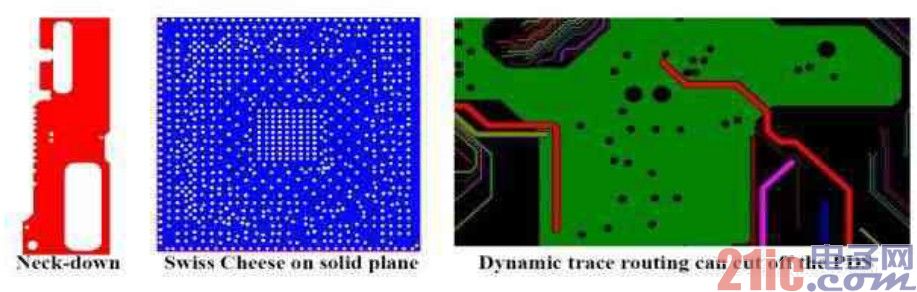

图1:PCB上一些常见的会增加电流路径阻性的物理结构设计。

电源地之间的输入阻抗概念就可以应用在对上述因素的仿真和分析中。比如,电源地输入阻抗的一个非常广泛的应用是用来评估板上去耦电容的放置问题。随着一定数量的去耦电容被放置在板上,电路板本身特有的谐振可以被抑制掉,从而减少噪声的产生,还可以降低电路板边缘辐射以缓解电磁兼容问题。为了提高电源供电系统的可靠性和降级系统的制造成本,系统设计工程师必须经常考虑如何经济有效地选择去耦电容的系统布局。

高速电路系统中的电源供电系统通常可以分成芯片、集成电路封装结构和PCB三个物理子系统。芯片上的电源栅格由交替放置的几层金属层构成,每层金属由X或Y方向的金属细条构成电源或地栅格,过孔则将不同层的金属细条连接起来。

对于一些高性能的芯片,无论内核或是IO的电源供电都集成了很多去耦单元。集成电路封装结构,如同一个缩小了的PCB,有几层形状复杂的电源或地平板。在封装结构的上表面,通常留有去耦电容的安装位置。PCB则通常含有连续的面积较大的电源和地平板,以及一些大大小小的分立去耦电容元件,及电源整流模块(VRM)。邦定线、C4凸点、焊球则把芯片、封装和PCB连接在了一起。

整个电源供电系统要保证给各个集成电路器件提供在正常范围内稳定的电压。然而,开关电流和那些电源供电系统中寄生的高频效应总是会引入电压噪声。其电压变化可以由下式计算得到:

这里ΔV是在器件处观测到的电压波动,ΔI是开关电流。Z是在器件处观测到的整个电源供电系统电源与地之间的输入阻抗。为了减小电压波动,电源与地之间要保持低阻。在直流情况下,由于Z变成了纯电阻,低阻就对应了低的电源供电IR压降。在交流情况下,低阻能使开关电流产生的瞬态噪声也变小。当然,这就需要Z在很宽的频带上都要保持很小。

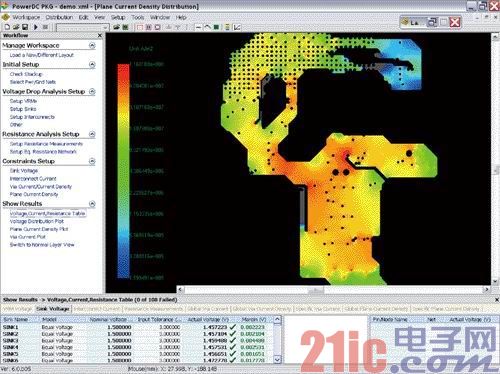

图2:Sigrity PowerDC计算得到电源板层上的电流分布。

注意到电源和地通常用来作为信号回路和参考平面,因此电源供电系统与信号分布系统之间有着很紧密的关系。然而,由于篇幅的限制,同步开关噪声(IO SSO)引入的电源供电系统的噪声现象和电流回路控制问题将不在这里讨论。以下几节将忽略信号系统,而单纯注重电源供电系统的分析。

直流IR压降

由于芯片的电源栅格(Power Grid)的特征尺寸很小(几微米甚至更小),芯片内的电阻损耗严重,因此芯片内的IR压降已经被广泛地研究。而在下面几种情况下,PCB上的IR压降(在几十到几百毫伏的范围内)对高速系统设计同样会有较大的影响。

电源板层上有Swiss-Chess结构、Neck-Down结构和动态布线造成的板平面被分割等情况(图1);电源板层上电流通过的器件管脚、过孔、焊球、C4凸点的数量不够,电源平板厚度不足,电流通路不均衡等;系统设计需要低电压、大电流,又有较紧的电压浮动的范围。

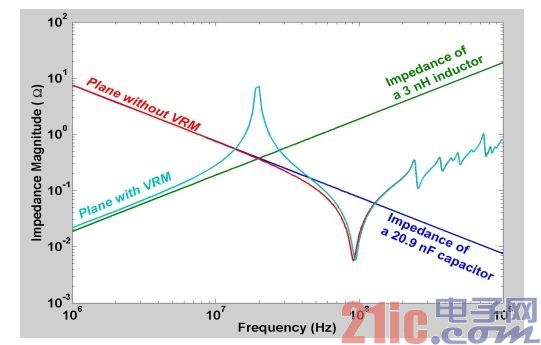

图3:包括和不包括电源整流模块的平板对输入阻抗。

例如,一个高密度和高管脚数的器件由于有大量的过孔和反焊盘,在芯片封装结构及PCB的电源分配层上往往会形成所谓的Swiss-Chess结构效应。Swiss-Chess结构会产生很多高阻性的微小金属区域。根据

,由于电源供电系统中有这样的高阻电流通路,送到PCB上元器件的电压或电流有可能会低于设计要求。因此一个好的直流IR压降仿真模拟是估计电源供电系统允许压降范围的关键。通过各种各样可能性的分析为布局布线前后提供设计方案或规则。

布线工程师、系统工程师、信号完整性工程师和电源设计工程师还可以将IR压降分析结合在约束管理器(constraint manager)中,作为对PCB上每一个电源和地网表进行设计规则核查的最终检验工具(DRC)。这种通过自动化软件分析的设计流程可以避免靠目测,甚至经验所不能发现的复杂电源供电系统结构上的布局布线问题。图2展示了IR压降分析可以准确地指出一高性能PCB上电源供电系统中关键电压电流的分布。

交流电源地阻抗分析

很多人知道一对金属板构成一个平板电容器,于是认为电源板层的特性就是提供平板电容以确保供电电压的稳定。在频率较低,信号波长远远大于平板尺寸时,电源板层与地板的确构成了一个电容。

然而,当频率升高时,电源板层的特性开始变得复杂了。更确切地说,一对平板构成了一个平板传输线系统。电源与地之间的噪声,或与之对应的电磁场遵循传输线原理在板之间传播。当噪声信号传播到平板的边缘时,一部分高频能量会辐射出去,但更大一部分能量会反射回去。来自平板不同边界的多重反射构成了PCB中的谐振现象。

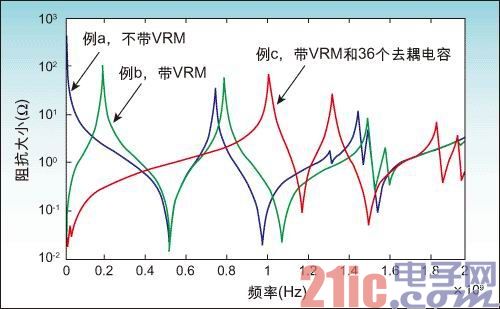

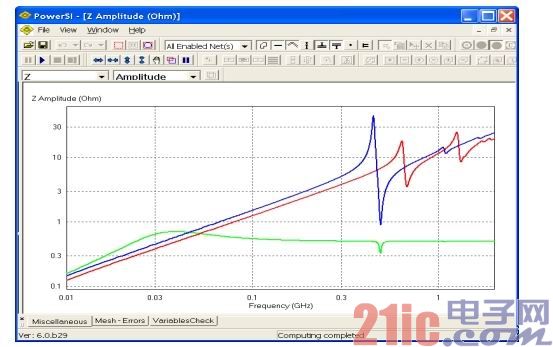

图4:三种设置情况下 PowerSI计算得到的PCB输入阻抗曲线。(a)不包含电源整流模块;(b)包含电源整流模块;(c)包含电源整流模块和一些去耦电容。

在交流分析中,PCB的电源地阻抗谐振是个特有的现象。图3展示了一对电源板层的输入阻抗。为了比较,图中还画了一个纯电容和一个纯电感的阻抗特性。板的尺寸是30cm×20cm,板间间距是100um,填充介质是FR4材料。板上的电源整流模块用一个3nH的电感来代替。显示纯电容阻抗特性的是一个20nF的电容。从图上可以看出,在板上没有电源整流模块时,在几十兆的频率范围内,平板的阻抗特性(红线)和电容(蓝线)一样。在100MHz以上,平板的阻抗特性呈感性(沿着绿线)。到了几百兆的频率范围后,几个谐振峰的出现显示了平板的谐振特性,这时平板就不再是纯感性的了。

至此,很明显,一个低阻的电源供电系统(从直流到交流)是获得低电压波动的关键:减少电感作用,增加电容作用,消除或降低那些谐振峰是设计目标。

为了降低电源供电系统的阻抗,应遵循以下一些设计准则:

1. 降低电源和地板层之间的间距;

2. 增大平板的尺寸;

3. 提高填充介质的介电常数;

4. 采用多对电源和地板层。

然而,由于制造或一些其他的设计考虑,设计工程师还需要用一些较为灵活的有效的方法来改变电源供电系统的阻抗。为了减小阻抗并且消除那些谐振峰,在PCB上放置分立的去耦电容便成为常用的方法。

图4显示了在三种不同设置下,用Sigrity PowerSI计算得到的电源供电系统的输入阻抗:

a. 没有电源整流模块,没有去耦电容放置在板上。

b. 电源整流模块用短路来模拟,没有去耦电容放置在板上。

c. 电源整流模块用短路来模拟,去耦电容放置在板上。

从图中可见,例子a蓝线,在集成电路芯片的位置处观测到的电源供电系统的输入阻抗在低频时呈现出容性。随着频率的增加,第一个自然谐振峰出现在800MHz的频率处。此频率的波长正对应了电源地平板的尺寸。

例子b的绿线,输入阻抗在低频时呈现出感性。这正好对应了从集成电路芯片的位置到电源整流模块处的环路电感。这个环路电感和平板电容一起引入了在200MHz的谐振峰。

例子c的红线,在板上放置了一些去耦电容后,那个200MHz的谐振峰被移到了很低的频率处(<20MHz),并且谐振峰的峰值也降低了很多。第一个较强的谐振峰则出现在大约1GHz处。由此可见,通过在PCB上放置分立的去耦电容,电源供电系统在主要的工作频率范围内可以实现较低的并且是平滑的交流阻抗响应。因此,电源供电系统的噪声也会很低。

图5:针对不同结构仿真计算得到的输入阻抗。不考虑芯片和封装结构(红线);考虑封装结构(蓝线);考虑芯片、封装和电路板(绿线)。

在板上放置分立的去耦电容使得设计师可以灵活地调整电源供电系统的阻抗,实现较低的电源地噪声。然而,如何选择放置位置、选用多少以及选用什么样的去耦电容仍旧是一系列的设计问题。因此,对一个特定的设计寻求最佳的去耦解决方案,并使用合适的设计软件以及进行大量的电源供电系统的仿真模拟往往是必须的。

协同设计概念

图4实际上还揭示了另一个非常重要的事实,即PCB上放置分立的去耦电容的作用频率范围仅仅能达到几百兆赫兹。频率再高,每个分立去耦电容的寄生电感以及板层和过孔的环路电感(电容至芯片)将会极大地降低去耦效果,仅仅通过PCB上放置分立的去耦电容是无法进一步降低电源供电系统的输入阻抗的。从几百兆赫兹到更高的频率范围,封装结构的电源供电系统的板间电容,以及封装结构上放置的分立去耦电容将会开始起作用。到了GHz频率范围,芯片内电源栅格之间的电容以及芯片内的去耦电容是唯一的去耦解决方案。

图5显示了一个例子,红线是一个PCB上放置一些分立的去耦电容后得到的输入阻抗。第一个谐振峰出现在600MHz到700MHz。在考虑了封装结构后,附加的封装结构的电感将谐振峰移到了大约450MHz处,见蓝线。在包括了芯片电源供电系统后,芯片内的去耦电容将那些高频的谐振峰都去掉了,但同时却引入了一个很弱的30MHz谐振峰,见绿线。这个30MHz的谐振在时域中会体现为高频翻转信号的中频包络上的一个电压波谷。

芯片内的去耦是很有效的,但代价却是要用去芯片内宝贵的空间和消耗更多的漏电流。将芯片内的去耦电容挪到封装结构上也许是一个很好的折衷方案,但要求设计师拥有从芯片、封装结构到PCB的整个系统的知识。但通常,PCB的设计师无法获得芯片和封装结构的设计数据以及相应的仿真软件包。对于集成电路设计师,他们通常不关心下端的封装和电路板的设计。但显然采用协同设计概念对整个系统、芯片-封装-电路板的电源供电系统进行优化分析设计是将来发展的趋势。一些走在电子设计前沿的公司事实上已经这样做了。